History of the RECEL Pinballs Here

Recel Sys III MPUs are the boards that run Recel's Spanish pinball machines. They first appeared in 1978 and power some fifteen versions of pinball machines created around that time.

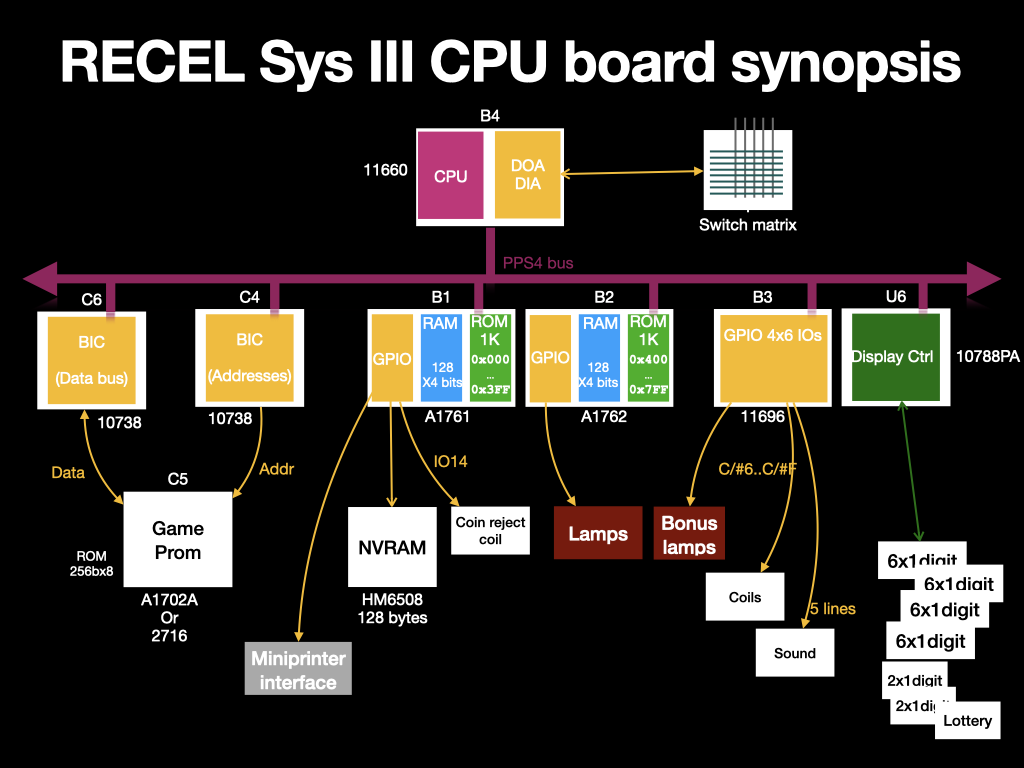

The architecture of a Recel system III is very similar to the one of Gottlieb Sys 1 machines. In particular, the CPU is 11660 PPS4/2. This is why these MPUs are presented here, and why we studied them and make clone of them.

The service manual (generic data, common to all versions) on this system is here

On the figure below is presented a synopsis of the Recel system 3 MPU. This allows us to identify which device controls which part of the system.

From the site lisy.dev, you'll find the complete schematic of the Master Unit, which is of great help to understand this system. Master board complete schematic

Making a clone is not just about understanding a general principle, it's also about understanding every detail and immersing yourself in its essence (The schematic). You can't start to clone something until all the dots are connected, until the whole landscape fits into its frame.

To do this, you need to spot unusual situations and, as in a police investigation, find out why.

The PPS4 instruction set is composed of 50 basic instructions. Most of them are straightforward, such as

LDI or ADI.

But, what about

CYS or SAG?

These instructions, for example, and a few others are more complex to handle, and therefore to translate into VHDL equivalent equations. A list of special cases with there full clarification is available through the following link:

Specific instruction behaviour

And, what is more unusual than IO15 of B2 being tied to VSS (aka +5V)? What can be the purpose of this strange design? Is it to be copied stricto censu for the clone? The explanation can be found in the self-test code for IOs of B1/B2. (around code address at 742). Actually, the code 2.4. which is declared in the service manual as "everything went well", states that IO15 of B2 cannot be reset.

Look at the chunk of schematic on the picture above. The red circle shows that IO-15 is permanently tied to +5V. This is exactly what the piece of code below expects from a healthy board.

;Beginning of Test IOs of B1/B2

;/!\ Something to be understood: when we arrive here

;we already have passed the init (namely 6C0 where all IO FF are set to 1

;then the first IOL 41 here shall return 1 because of that

;C=0 => device 4 is addressed, else device 2

;FF1==1=> turn 1: set output to 0, and expect to read current state to 1

;because on entry of this routine all output FF are initialized to 1

;FF1==0=> turn 2: set output to 1 and expect to read 0, which was put

;there during previous turn of IOL (when FF1 was 1)

;start with RC, SF1, ie device 4, set output to 0,

734 24 RC ; Reset Carry flip-flop

735 B7 T 737 ; Transfer

736 20 SC ; Set Carry flip-flop

737 22 SF1 ; Set FF1

;set all IOs as output (SES 1)

738 70 LDI F ;

739 1C 20 IOL 20 ; 2 is B2 aka A1762, SES 1: enable all output

73B 70 LDI F ; Load Accumulator Immediate

73C 1C 40 IOL 40 ; 4 is B1 aka A1761, SES 1: enable all output

;goto first test:

;C determine if we address device 4 or 2

;FF1 determine if we are testing IO for 0 (+5V) or 1 (-12V)

73E 57 44 TL 744 ; Transfer Long

740 57 36 TL 736 ; Transfer Long

;we are doomed, the last test failed (read != written)

742 22 SF1 ; Set FF1

743 9E T 75E ; Transfer

;very first time here C=0 FF1=1: set out to 0 and verify current is 1

744 16 SKF1 ; Skip if FF1 Equals 1

;we are going to set the current IO to 1

745 77 LDI 8 ; Load Accumulator Immediate

;very first time here (C=0, F1=1)

;we are going to set the current IO to 0

746 7B LDI 4 ; Load Accumulator Immediate

747 1B LXA ; Load X Register from Accumulator

;store 8 or 4 into BM which will be a parameter for the display routine

748 18 XBMX ; Exchange BM and X BM will contain 4 or 8 and will be used in case of failure as param for code display

749 15 SKC ; very first time (vft): no skip because C=0

;depending on C, we will address IOs of B1 or B2

74A 8E T 74E ; Transfer test B1

74B 1C 21 IOL 21 ; test B2

74D 90 T 750 ; Transfer

74E 1C 41 IOL 41 ; on vft Acc->4, Acc<-1xxx

; because IO F/F0 was initialised to 1 (6C0)

750 16 SKF1 ; Skip if FF1 Equals 1. SKIP on vft

751 66 ADI 9 ; Add Immediate and skip on carry-out, execute this only on 1st turn (FF1=1)

752 66 ADI 9 ; on vft A<-A+9 with A=1xxx=>skip

; but on 2nd turn (FF1=0), we expect

; output is 0 as it was set during first turn

; if it is 0, no skip on the first ADI,

; hence skip on the 2nd ADI, outp is OK

; if it is 1, it is not normal and it will skip

; on the first ADI, skipping the 2nd ADI,

; landing at the error routine call

;T 742: the ouput is not read as it was written at t-1=>display io error, BM:error type, BL: #IO, A: #device

;the simulator should reply b1xxx when FF1==1, or b0000 when FF1=0

753 82 T 742 ; Transfer to display error. BL contains the erroneous IO

754 17 INCB ; ;select next #IO and loop back

755 84 T 744 ; Transfer to next IO test

;all IOs tested

;if both voltage level were checked

756 16 SKF1 ; Skip if current turn is turn 1, go ahead with turn 2

757 9A T 75A ; Transfer

;start again with other polarity test

758 26 RF1 ; Reset FF1, to indicate start of turn2

759 84 T 744 ; Transfer to entry loop for turn 2

;start again with the other device or we are done

75A 15 SKC ; Skip on Carry flip-flop, we are done

75B 80 T 740 ; rexecute test turn 1, 2 for device B2

;everything went well...

;/!\ but it is not possible to go well

;because IO15 of B2 is permanently tied to +5V

;(thank you Ralf, for this one)

;hence the display is 2.4.. for B2 IO#F failed

75C 00 FF LBL 000 ; Load B Long

;There are 2 ways to reach 75E: 1/everything went well, 2/a test failed from 742

;select #device causing failure, or 2 if all ok

75E 15 SKC ; Skip on Carry flip-flop

75F 7E LDI 1 ; Load Accumulator Immediate

760 7D LDI 2 ; Acc<-2 when all tests passed

;36A display seltest (act. 78D)

761 03 6A TML 36A ; Transfer and Mark Long

;Play short tone

;as mentionned in the operator manual p3.3, middle line

763 70 LDI F ; Load Accumulator Immediate

764 1C D3 IOL D3 ; Input/Output Long

766 01 D2 TML 1D2 ; Transfer and Mark Long

768 7F LDI 0 ; Load Accumulator Immediate

769 1C D3 IOL D3 ; Input/Output Long

;goto next test (open or short of coils)

76B 57 C0 TL 7C0 ; Transfer Long

There are 2 Hardware version of the System III:

| Device | Start addr. | End addr. | Dev. CS | Dev. start @ | Dev. End @ | Size |

| A1761 | 0x000 | 0x3FF | RRSEL<=not (AB11 | AB12) | 0x000 | 0x3FF | 1KB |

| A1762 | 0x400 | 0x7FF | RRSEL<=AB11 | 0x000 | 0x3FF | 1KB |

| Game prom 1702A | 0x800 | 0x8FF | BIC CS<=AB12 | 0x000 | 0x0FF | 256B |

| Device | Start addr. | End addr. | Dev. CS | Dev. start @ | Dev. End @ | Size | |

| A1761 | 0x000 | 0x3FF | RRSEL<=not (AB11orAB12) | 0x000 | 0x3FF | 1KB | |

| A1762 | —— | —— | OFF (RRSEL tied to VSS) | 0x000 | 0x3FF | 1KB | |

| 2716 1st half | 0x800 | 0xBFF | BIC CS<=AB11 | AB12 | 0x000 | 0x3FF | 1KB | Game area |

| 2716 2nd half | 0x400* | 0x7FF* | BIC CS<=AB11 | AB12 | 0x400 | 0x7FF | 1KB | Alt. A1762 |

(*) This area is mirrored in range 0xC00..0xFFF, as well, from the CPU point of view.

The remarkable point is that the mod to apply for going from HW version1 to version 2 is super easy. B2's RRSEL is to be tied to VSS permanently so that its ROM subsection is disabled. Then the very signal which is originally connected to B1's RRSEL, is also to be connected to the chip select of address BIC (C4). Then, the address range of the game prom will be 0x800..0xBFF and 0x400..0x7FF (as a mirror of 0xC00..0xFFF).

Version 2 can implement any game. To run a game of V1 on V2, just program a 2716 with the game prom in first half and a copy of A1762 content in second half.

Things get more complicated when you realise that version 1 hardware can also be found with a 2716. In this case people simply used a 2716 in replacement of a 1702A, because 1702A are hard to find, and even harder to program by these days, while a 2716 has the same behaviour as a 1702A in readings, but easy to reprogram. Hence, having a 2716 fitted on the game prom location is not an evidence of hardware V2. Having a 1702A on the board on the contrary is the evidence that we are in presence of a HW type 1.

Binary data (In B1, B2, or eprom) are PPS4 assembly code. Since, the eprom is accessed through BIC interface, and also because PPS4 logic is negative, you won't read pps4 assembly code directly from a .c5 file. If you want to disassemble this data, you need to invert both addresses and data first. Then, you'll get PPS4 mnemonics. Since game proms are read by the MPU through PPS4 BIC chips, which use negative logic, you have to invert both addresses and data to make a bin image from a '.c5' file. Since game proms are read by the MPU through PPS4 BIC chips, that use negative logic, you have to invert both addresses and data to make a bin image from a '.c5' file.

When making a replacement game prom, either for a version 1 or 2, keep in mind that PPS4 uses a negative logic. Then you will have to reverse both addresses and data of the binary before flashing it to your prom. This is because the eprom will be access through the address and data BICs.

In summary, to make game prom, use .c5 files. To disassemble or use directly the code with, for example, an emulator, you'll have to make the double inversion thing.

Please, remember that you must be logged on in order to be able to download files from this table. Or, you can get all files at once from github.

Binaries of all Recel games Here

Readme.md Here

or use the command: git clone https://github.com/garzol/RECEL.git

| Name | Model# | A1762 version | Game binary | Game sz | |

| Alaska | ? | A1762-13_1K.bin | al.bin | 256B | |

| Black magic 1P(*) | 1065 | bmA1762.bin (+) | bmgame.bin | 1KB | 1player |

| Black magic 4P(**) | 1066 | b4A1762.bin (+) | b4game.bin | 1KB | 4player |

| Cavalier | 1062 | A1762-13_1K.bin | ca.bin | 256B | |

| Crazy race | 1054 | crA1762.bin | crgamex4.bin (i) | 1KB | 4 times the same 256B |

| Fair-fight | 1053 | A1762-13_1K.bin | fa.bin | 256B | |

| Hot&cold | ? | A1762-13_1K.bin | hc.bin | 256B | |

| The flipper game | ? | flA1762.bin | flgame.bin | 1KB | |

| Mr Doom | 1060 | A1762-13_1K.bin | md.bin | 256B | |

| Mr Evil | 1055 | A1762-13_1K.bin | me.bin | 256B | |

| Pokerplus (***) | 1051 | A1762-13_1K.bin | pokerplus_BA65.BIN | 256B | |

| D. Quijote | 1063 | A1762-13_1K.bin | qu.bin | 256B | |

| Screech (****) | 2004 | A1762-13_1K.bin | sc_1_1702.bin | 256B | |

| Swashbuckler | 1061 | A1762-13_1K.bin | sw.bin | 256B | |

| Torneo | 1056 | A1762-13_1K.bin | to.bin | 256B |

(*) Black magic exists in 2 forms: 1-Player and 4-Player. In both cases, the game prom size is 1KB, hence Black magic requires version 2 HW

(+) The A1762 versions of Black magic are noted bmA1762.bin and b4A1762.bin resprctively. These are the binaries that we've read from the corresponding zip files (from Mame). They are actually identical to the original A1762 bin. We call them with a specific name for each, but their content are identical.

(i) Crazy race binary game from Mame zip has a size of 1KB. It's actually four times the same block of 256 bytes. We called this file "crgamex4.bin". Crazy race game is compatible with original A1762 bin. In this case, the selftest will execute the same way as other HX version 1 games, namely with PIO test and bonus lamp test. These tests are skipped if you use the crA1762.bin version of the A1762.

(***) Be careful, po.bin coming from Mame zip file is wrong. Use pokerplus_BA65.BIN instead. File given by recreativas.org (CRC confirmed by lisy.dev)

(****) Screech has a unique behaviour, compared to the other games. There is no attract mode (we ignore why, maybe it's an early game?). Coils (not all) are protected from permanent on state. For example the ball home rejector will alternate on and off at around 5Hz (while BH switch forced to open). On other games, in similar situation, the ball home rejector keeps staying on until the retriggerable fuse cut power.

On the Mame Github Here we picked also the following information:

| IOL code | #U | Device Type | Role |

|---|---|---|---|

| b1101 (0xD) | B3 | 11696 | PIO |

| b0100 (0x4) | B1 | A1761-13 | Access NVRAM HM6508+few output control |

| b0010 (0x2) | B2 | A1762-13 | 16 outtput control |

| b1111 (0xF) | B5 | 10788PA | Display control |

(2023-11). Thanks to Paulo, one of our nice visitors on this site, who agreed to lend us the two spiders of RECEL (A2361&A2362) where the code resides, we eventually were able to read the program that runs RECEL pinballs. As an easter egg, Paulo also sent us a game eprom (for screech) we also read (1702 eprom from 1972, weird chip) and archived on github. This material is now (for the first time) available to the community.

Binaries of Recel Here

or use the command: git clone https://github.com/garzol/RECEL.git

Commented code disassembly Here

Eduardo, from recreativas.org, later (2023-12) sent us another variant for these 2 chips, namely A1761-14 and A1762-14 (variant 14 instead of 13). We returned him the set as promised after a few days, the time for us to read their contents. We read the 14 variant and found the exact same contents as for the previous 13 variant.

Therefore we can safely assert that variant 13 and 14 of these chips are strictly identical.

Now that we have everything to make clones of A1761s and A1762s we have all we need to repair any Recel System III.

There are few situations where we will be facing a dead end. In such a case, the solution is our MPU Clone. Our MPU Clone is really identical to the original Receel sys 3 MPU. The only difference is that ours is just much more reliable than the original. In term of functionality they are really impossible to distinguish. Dimension, connectics, all is same.

If the processor is dead, the only solution is to find a good one in replacement. We have all we need to clone a PPS4 processor. But we are proably not going to. The only problem is that it would cost as much as a complete clone, maybe more. This is because of the -12V, +5V power supply it requires, which implies a big number of MOSFETs to comply with that.

If the 10788 is dead, you can use one of our 10788 clone from here

If the 11696 is dead, this is the same comment as for the processor. We know how to clone them, but, again, its cost would be superior to the one of a complete MPU clone.

If you identified that your problem comes from a BIC, an A1761 or an A1762, then we have a solution for you.

Therefore, our MPU clone is the universal solution to a failing or dead original MPU. Much more comfortable for your nerves in the end! Should you have any question, please contact us Here and explain your problematic. We will reply quickly and exchange by email to see how we can solve your problem.

With our clone (either a device clone or a complete MPU clone) you'll have even more advantages: you'll have a wifi interface that allows you to read information about the pinball in real time:

If the problem is related to one A17, or both of them, the only thing we have to do is to replace one or both by one or two clones, just as we do for Gottlieb system I.

If the problem is related to one BIC, or both of them, this is where the beauty of our solution resides: BICs are only used for interfacing the eprom. By integrating the eprom contents right in our clone, we will interface the 256 bytes of the eprom internally. All you have to do is replacing any A17 by its clone, and pulling out the 2 BICS to prevent bus contention. And that's it. One single clone will play the role of the A17+the 2 BICS+the eprom. The code in ROM is unchanged!

For any other kind of problem, we recommend you to acquire a Recel S3 Clone from our site.

Ready to check it out?

We also made a model of the System 3 sound section. More infos Here

This video shows a working Fair fight, which implements 2 A17 clones:

This video shows the supervisor mode of WiFlip in action:

Now that you've bought a brand new Master Unit clone for your Recel S3 pinball machine, you should be less than a stone's throw away from a well-deserved good game and fun.

But, don't forget that there still are 3 other boards inside the pin: power board, mux board, and display unit. That makes a lot of potential sources of malfunction. The first reflex you should have is to make use of WiFlip

Before pulling out the big guns, you can look at this FAQ page which list the main situations you'll frequently encounter with these machines.