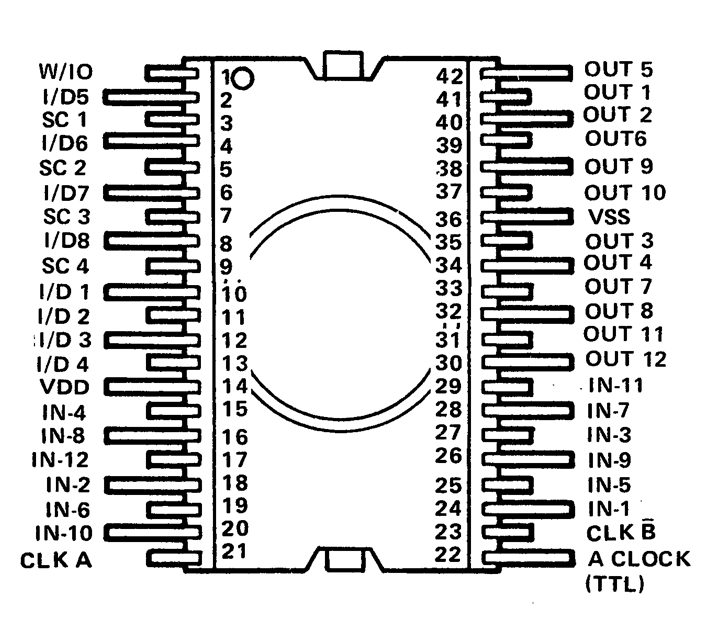

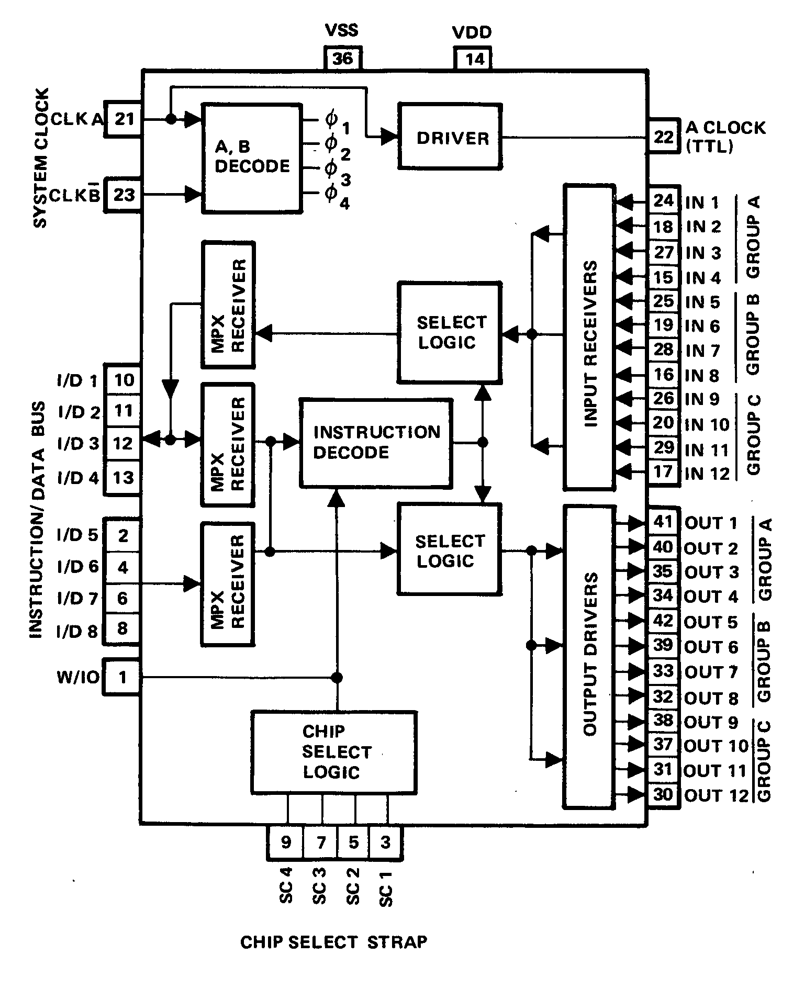

The 10696 is a PPS4-1 general purpose IO. Its synopsis is described on the figure below.

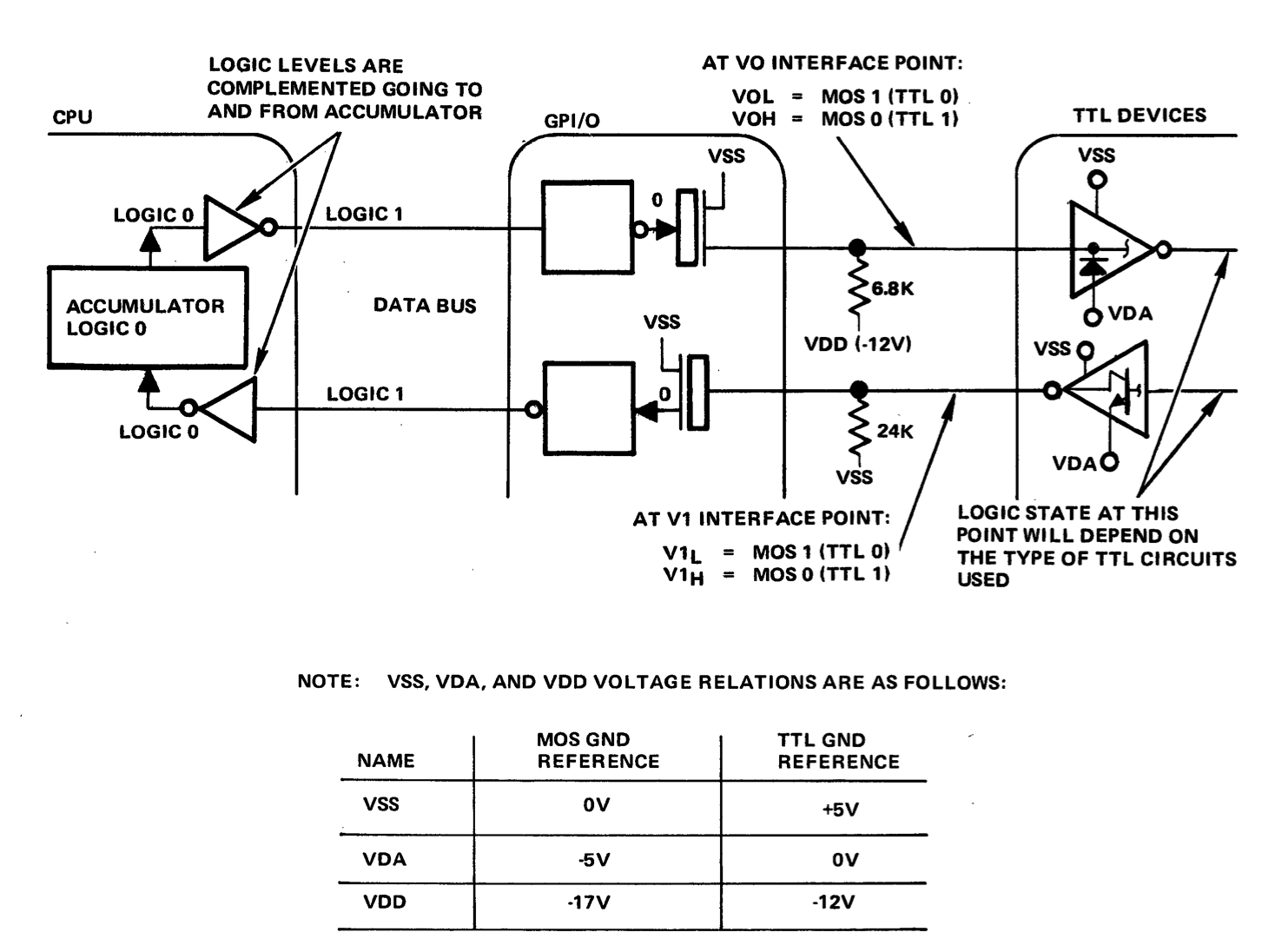

The 10696 provides 12 discrete inputs and 12 discrete static outputs. This device is used for direct data exchange or status and control functions with an external peripheral device. This device is directly compatible with TTL, provided that you don't forget that PPS4 has a negative logic. Resistances between MOS and TTL must be fitted to avoid problems. See figure below.

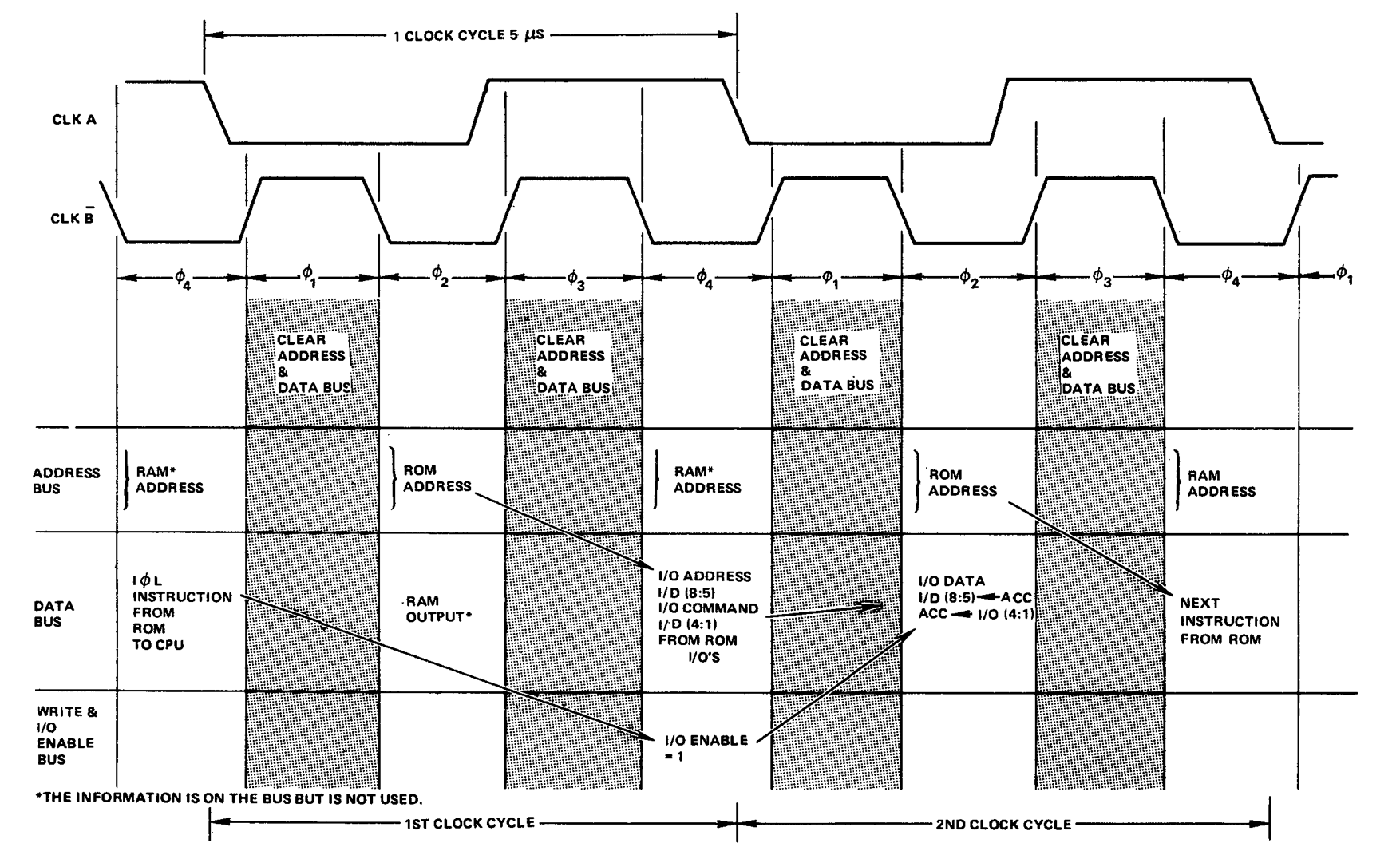

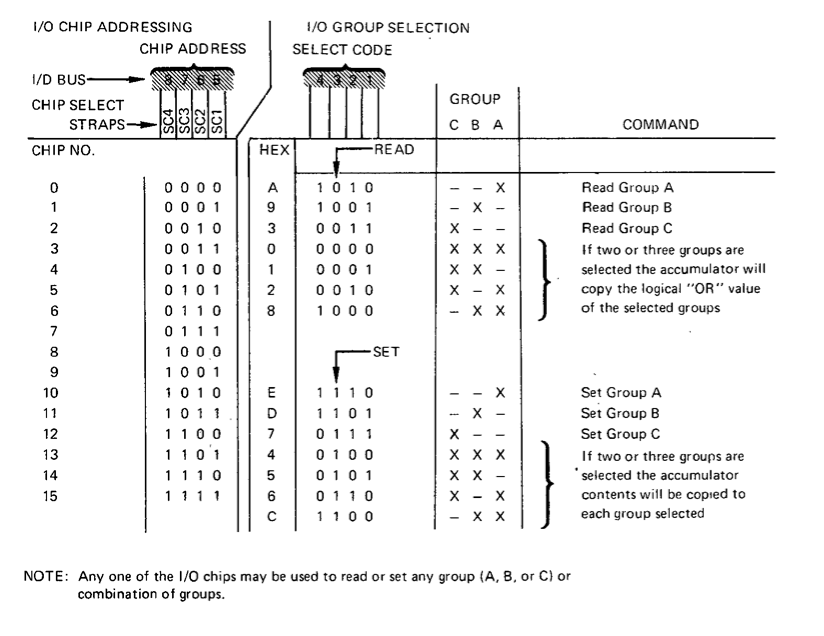

Direct addressing for up to 16 of these circuits is possible by the use of 4 chip address straps that can be terminated, by the user, to create each chip address. The I/O is accessed with an I/O enable signal from the CPU and a simultaneous 8-bit instruction from ROM. 4 bits of the instruction are used to address the particular I/O chip (I/D5..8 is the device ID); the other 4 bits define the I/O operation (I/D1..4 is the command).

The 4-bit operation code is interpreted by the I/O to either copy the contents of the accumulator into one of the 3 4-bit parallel output registers (A, B or C) or transfer data from 1 of the 4-bit parallel input receivers (A, B or C) into the accumulator of the CPU. The output drivers are static outputs and data remains in the output registers until altered. The command is coded as below:

Data is transferred through the GPI/O from input groups A, B or C to I/D1..4 and output groups A, B or C to I/D5..8 most significant to most significant and least significant to least significant.